A well known aspect of constraint solving is the ability to classify hard vs. soft constraints. A quick Google search on “soft constraints” would lead you to; http://www.constraintsolving.com/tutorials/soft-constraints-tutorial in case you are interested in theory.

Taking a practical example, given the holiday season around the corner many of us would like to travel, book tickets etc. Let’s say that we want to travel from City-1 to City-2 (Say Bangalore to Chennai); the source & destination are fixed and are non-negotiable. But how we travel can be based on preference/availability/cost etc. For instance one may have options of:

- Flight

- Bus

- Train

- Car

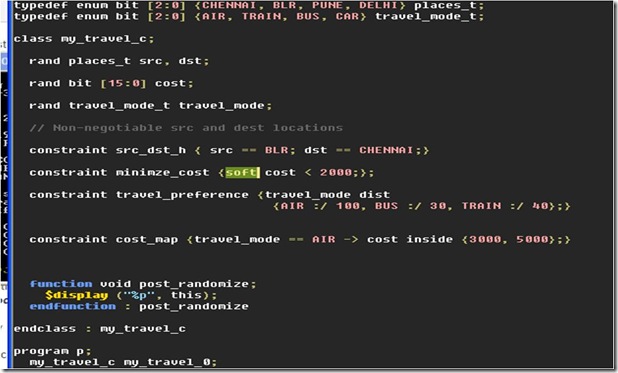

Now modeling the above scenario using a constraint specification language like the one in SystemVerilog, there are “constraints” as below;

class my_travel_c;

rand places_t src, dst;

rand int cost;

rand travel_mode_t travel_mode;

// Non-negotiable src and dest locations

constraint src_dst_h { src == BLR; dst == CHENNAI;}

constraint minimze_cost { cost < 2000;};

constraint travel_preference {travel_mode inside {AIR, BUS, TRAIN};}

endclass : my_travel_c

Now depending on various factors the cost & travel-mode constraints may not be solvable. For instance if only AIR travel is desired, the cost constraint is likely to be violated. As an avid traveler you may not mind that violation and say YES it is fine! But how do you tell that to SystemVerilog? In the past one may go and turn-off the relevant/violating constraint via constraint_mode(0);

However that becomes tedious as before every randomize call you would need to do it (perhaps across testcases).

Welcome the all new System Verilog 2012 soft constraint:

Now if the solver can satisfy the SOFT it shall, and provide you the optimal cost and travel experience. However in case it can’t, the soft can be “ignored” and other HARD constraints shall be obliged!

Now that’s a pleasure luxury to have a set of “default” values while designing the environment and use “soft” constraints, let the tests/scenarios override the same as needed.

BTW – this has been a widely used feature in e – IEEE-1647 language (many engineers relate it to the tool Specman, most popular implementation of the e language). So much so that a new user migrating from Specman to SystemVerilog finds it often annoying not to have this “feature”. Now, thanks to Santa in 2012, come 2013 – you will have that in SV too! Now it is time to ask for your XMAS wish with Santa and your EDA vendor to get this implemented in your favorite simulator!

Have a pleasant journey, holidays and be ready to rock even more with all the more powerful SystemVerilog 2012 soon!

No comments:

Post a Comment